**Product Data Sheet**

# SRM-155 SONET/SDH Fiber-Optic Receiver Module with SAW Filter Clock Recovery and Data Retiming

The SRM-155 SONET/SDH Fiber-Optic Receiver Module

### **Features**

- SONET OC-3 and SDH STM-1 Compatible

- SAW Filter Clock Recovery and Data Retiming

- 17 ps Typical Output Jitter

- PECL Clock and Data Outputs

- Single +5 Volt Supply

- CMOS Loss of Signal Flag

- Operation at 1300 nm and 1550 nm

- -45° to +85°C Operation

- Wide Dynamic Range

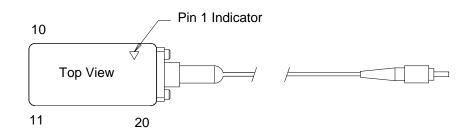

- Multi-Sourced 20 Pin DIL Footprint

# Applications

- Telecom Receiver Applications Medium and Long Haul SONET/SDH @ 155 Mb/s

- High Performance Datacom Receiver Applications ATM @ 155 Mb/s

# Description

VTI's SRM-155 is a fully integrated fiber-optic receiver module with SAW filter clock recovery and data retiming. It is ideally suited for SONET OC-3, SDH STM-1 and other 155 Mb/s fiber-optic transmission applications that demand superior performance and stability.

### **Functional Overview**

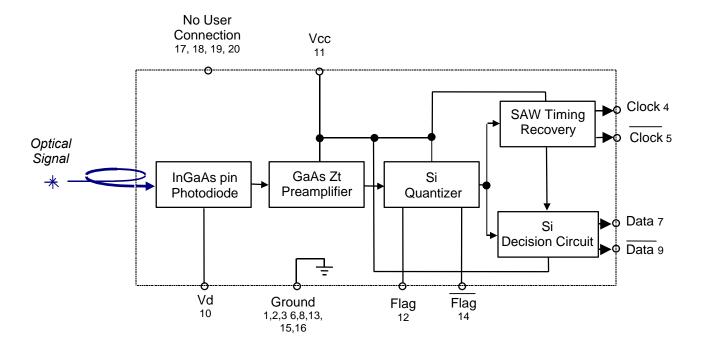

This highly integrated module converts a 155 Mb/s fiber-optic NRZ signal to differential PECL recovered clock and retimed data outputs. A CMOS flag alerts the user to a loss of signal condition when the optical input falls below an acceptable level.

A single +5 Volt supply provides bias for the module's pin-photodiode, preamplifier, Quantizer, and SAW filter timing recovery circuit. All elements are integrated into fiber-coupled 1.3" X 0.635" 20 pin DIL package. The SRM-155 footprint and pinout are industry common for ease of integration.

The optical signal is coupled through a short length of SBJ, Type 2, 62.5  $\mu$ m multimode optical fiber to a hermetic module which encases an InGaAs pin-photodiode and preamplifier. The pin-photodiode converts the optical signal to an electrical current. The signal is then converted to a voltage and amplified by a low noise transimpedance amplifier. Further gain is provided by the quantizer, which also provides a Flag output when the optical signal falls below an acceptable

level. The signal is then input to a SAW-filter timing recovery circuit where the the clock signal is recovered, and the data signal is reshaped and retimed.

The clock recovery and data retiming function is achieved using a SAW filter technique which is well established and proven through years of application in high performance telecom systems.

The clock is extracted from the input NRZ data by first passing it through a frequency doubler to generate sufficient spectral energy at 155 MHz. The SAW filter, a precision narrow band filter, then suppresses jitter by rejecting unwanted frequency spectrum. The extracted clock is then precisely aligned with the data and the signals are reshaped.

The output signal is thus free of undesirable jitter and distortion. Unlike phase-looked loop designs, the jitter transfer function of the SRM-155's timing recovery circuit is uniquely stable because it is determined by the shape of the SAW filter's response, which can be precisely controlled. In addition to low output jitter and excellent stability, the SRM-155's timing recovery circuit exhibits fast acquisition time and robust operation

Figure 1. SRM-155 Functional Block Diagram

### SRM-155 SONET/SDH Receiver Module Product Data Sheet

#### Figure 2. Pin Diagram (Top View)

#### Table 1. Pin Function

| Pin                | Symbol          | Function                                                                                                                                     |  |  |  |

|--------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4                  | Clock           | PECL Recovered Clock Output.                                                                                                                 |  |  |  |

| 5                  | Clock           | PECL Complementary Recovered Clock Output.                                                                                                   |  |  |  |

| 7                  | Data            | PECL Retimed Data Output.                                                                                                                    |  |  |  |

| 9                  | Data            | PECL Complementary Retimed Data Output.                                                                                                      |  |  |  |

| 10                 | VD              | Detector Anode Bias. Ground or apply +5 Volt bias through a series resistor for received optical power monitoring. <sup>1</sup>              |  |  |  |

| 11                 | V <sub>cc</sub> | 5 Volt Supply Voltage.                                                                                                                       |  |  |  |

| 12                 | Flag            | Input Signal Level Status. This CMOS output switches low when the received optical power falls below the status minimum optical power level. |  |  |  |

| 14                 | Flag            | Complementary Input Signal Status. CMOS complement of Flag.                                                                                  |  |  |  |

| 1,2,3,6,8,13,15,16 | GND             | Ground.                                                                                                                                      |  |  |  |

| 17,18,19,20        | NC              | No User Connection.                                                                                                                          |  |  |  |

1. By connecting pin 10 to a +5 Volt bias through a series resistor (eg. 1 kΩ) received optical power can be monitored as a voltage drop across the resistor.

### **Absolute Maximum Ratings**

Absolute maximum ratings are provided here as worst case and short duration exposure conditions only. Exposure to conditions more severe than the Absolute Maximum Ratings may result in permanent damage. Exposure to conditions at the Absolute Maximum Ratings for extended periods may also adversely affect device performance or reliability. Functional operation of the device is not implied at these conditions.

#### Table 2. Absolute Maximum Ratings

| Parameter                 | Symbol          | Minimum | Maximum | Units |  |

|---------------------------|-----------------|---------|---------|-------|--|

| Storage Temperature Range | Ts              | -40     | 85      | °C    |  |

| Supply Voltage            | V <sub>cc</sub> | 0       | +6      | V     |  |

| pin Detector Bias         | V <sub>D</sub>  | 0       | +6      | V     |  |

| Lead Soldering Conditions |                 |         | 250/10  | °C/s  |  |

# **Performance Characteristics**

#### **Table 2. Electrical Performance**

| Parameter                                              | Symbol                         | Minimum                | Typical | Maximum                | Units  |

|--------------------------------------------------------|--------------------------------|------------------------|---------|------------------------|--------|

| Input Signal Rate <sup>1</sup>                         | f <sub>O</sub>                 | 155.489                | 155.520 | 155.551                | Mb/s   |

| Operating Temperature                                  | To                             | -40                    |         | +85                    | °C     |

| Power Supply Voltage                                   | V <sub>cc</sub>                | 4.5                    | 5.0     | 5.5                    | V      |

| pin Detector Bias Voltage (pin10)                      | VD                             | 0                      | 0       | +5                     | V      |

| Power Supply Current                                   | Icc                            |                        |         | 300                    | mA     |

| Data and Clock Output Levels <sup>2</sup>              |                                |                        |         |                        |        |

| Low                                                    | V <sub>OL</sub>                | V <sub>CC</sub> - 1.95 |         | V <sub>CC</sub> - 1.63 | V      |

| High                                                   | V <sub>OH</sub>                | V <sub>CC</sub> - 1.03 |         | V <sub>CC</sub> - 0.88 | V      |

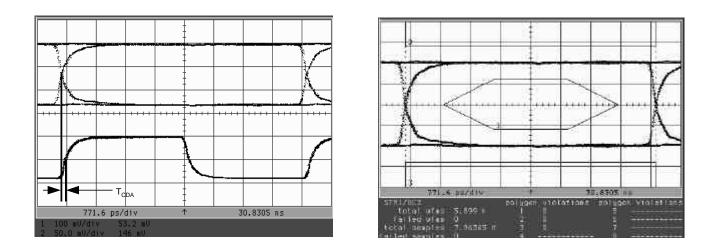

| Clock to Data Alignment <sup>3</sup>                   | T <sub>CDA</sub>               | -100                   |         | +100                   | ps     |

| Data and Clock Output Rise and Fall Times <sup>4</sup> | T <sub>R,</sub> T <sub>F</sub> | 275                    | 375     | 575                    | ps     |

| Output Clock Duty Cycle                                | Duty                           | 45                     | 50      | 55                     | %      |

| Received Power Level Flag                              | LOS                            |                        |         |                        |        |

| Decreasing Optical Power                               |                                |                        | -37     |                        | dBm    |

| Increasing Optical Power                               |                                |                        | -34     |                        | dBm    |

| Flag Hysteresis                                        | Hyst                           |                        | 3       |                        | dB     |

| Acquisition Time <sup>5</sup>                          | T <sub>A</sub>                 |                        |         | 2                      | μs     |

| Output Clock Random Jitter <sup>6</sup>                | Jc                             |                        | 17      |                        | ps rms |

1. Other center frequencies are available in the 124 to 622 MHz frequency range. Please contact t VTI for further details. 2. Measured with a load of  $R_L = 50\Omega$  to  $V_{cc} - 2$  V. See figures 3 and 4. ECL levels are specified for dc measurement, an additional tolerance of 50 mV should be included for dynamic measurements.

+5 V

a. Alignment of clock and data outputs (see Figure 5.).

a. Measured at 20% to 80% levels.

5. Time required to achieve valid data and clock outputs with a transition density of at least 50%.

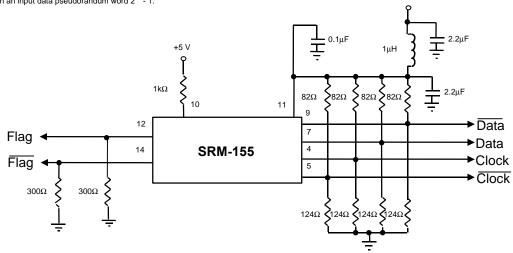

b. Measured with an input data pseudorandum word 2<sup>23</sup> - 1.

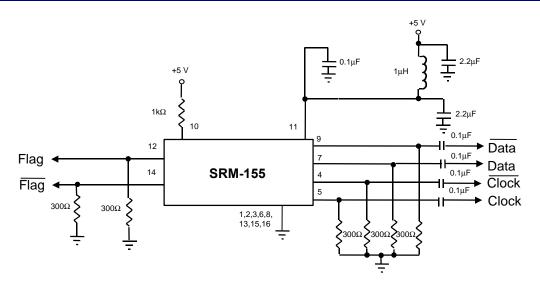

Figure 4. ECL (AC Coupled) Interface

Figure 5. Typical Performance

#### **Table 3. Optical Performance**

| Parameter                                | Symbol           | Minimum | Typical | Maximum | Units |

|------------------------------------------|------------------|---------|---------|---------|-------|

| Minimum Average Sensitivity <sup>1</sup> | Sens.            |         |         | -34.0   | dBm   |

| Maximum Optical Input <sup>1</sup>       | P <sub>MAX</sub> | 0       |         |         | dBm   |

| Input Wavelength                         | λ                | 1100    |         | 1580    | nm    |

1. For a BER less than 1E-10. Measured using a 2<sup>23</sup> - 1 pseudorandum word and a 50% average optical duty cycle and a 10 dB Extinction Ratio.

### Qualification

The SRM-155 has been designed to comply with the intent of Bellcore specifications TR-NWT-000468 and TA-TSSY-000983 and will be subject to a complete qualification test plan to demonstrate full compliance. All of the technologies used in the assembly of the module represent standard microelectronics technologies that are used in similar products, and have extensive field reliability data.

While all components and technologies used in the optical receiver are backed by qualification data and should present no reliability risk, VTI intends to qualify the fully assembled module with the final design. The qualification plan will entail mechanical and environmental tests along with accelerated life tests. The tests will include those parameters listed below.

#### Table 4. Qualification Plan

| Parameter                     | Test Method                      | Sample Size |

|-------------------------------|----------------------------------|-------------|

| Physical Dimensions           | MIL-STD-883, Method 2016         | 11          |

| Mechanical Shock              | MIL-STD-883, Method2007, Test B  | 11          |

| Vibration, variable frequency | MIL-STD-883, Method 2007, Test A | 11          |

| Lead Solderability            | MIL-STD-883, Method 2003         | 22          |

| Lead Integrity                | MIL-STD-883, Method 2004         | 15          |

| Temperature Cycling           | -40°C/85°C, 300 cycles           | 11          |

| High Temperature Aging        | 85°C under bias, 3000 hours      | 11          |

| Low Temperature Storage       | -40°C, 168 hours                 | 11          |

| ESD                           | Method 3015                      | 3           |

| Destructive Bond Pull         | MIL-STD-883                      | 40          |

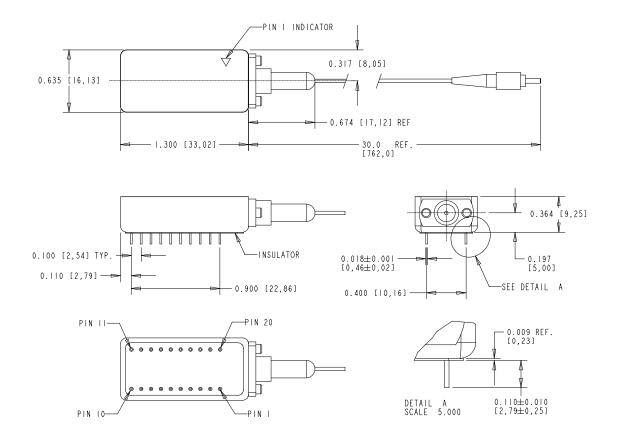

# **Optical Fiber Characteristics**

The fiber pigtail is a 30.0 +/-1 inch (measured from the package case to the connector tip) Type 2A multimode fiber with a 62.5 um core. The fiber is encased in a slate colored Strengthened Buffered Jacket (SBJ) cable sheath having a 900 um outer jacket diameter. The minimum fiber bend radius is 1.25 inches. Connectors may be selected to meet the specific requirements of each application.

### SRM-155 SONET/SDH Receiver Module Product Data Sheet

# **Outline Diagram**

Figure 5. Outline Diagram

### **Ordering Information**

#### Table 5. Part Numbers

| Fiber-Optic Connector <sup>1</sup> | Model Number | VTI Code Number |

|------------------------------------|--------------|-----------------|

| None                               | SRM-155      | 330001595       |

| FC/PC                              | SRM-155A     | 330001702       |

| ST                                 | SRM-155B     | 330001710       |

| SC                                 | SRM-155C     | 330001728       |

1. Other connectors or fiber requirements are available to meet specific application requirements.

Notes:

#### For Additional Information Please Contact:

Vectron Technologies, Inc. 267 Lowell Road Hudson, NH 03051 Tel: (603) 598-0070 Fax: (603) 598-0075

Vectron Technologies, Inc. reserves the right to make changes to the product(s) and/or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Rev. 0.1, 3/14/97 MDC, /:SRM155F2.SD